## Department of Electrical and Computer Engineering

## CANDIDACY EXAM: Circuits and Electronics

Time: 3 hours (9:00 AM – 12:00 noon)

Name:\_\_\_\_\_

Student number:\_\_\_\_\_

Student's signature:\_\_\_\_\_

## **General Instructions:**

- 1. This is a closed-book exam. No formula sheet is allowed.

- 2. There are a total of ten problems, Q1-Q10, in this exam. You are to choose only six problems for marking. On the list below circle the problems you want marked and only those will be marked. If none are circled the first six will be marked.

- 3. No large memory programmable calculators are permitted.

- 4. Cell phones and other wireless devices must be turned off.

- 5. You will be provided with scrap paper.

- 6. Make sure that your name, student number, and signature are written on this page.

| Q1:         | /10  |

|-------------|------|

| Q2:         | /10  |

| Q3:         | /10  |

| Q4:         | /10  |

| Q5:         | /10  |

| Q6:         | /10  |

| Q7:         | /10  |

|             | /10  |

|             | /10  |

| -           | /10  |

| -           | / 50 |

| 1 () 1 / 1L | / 50 |

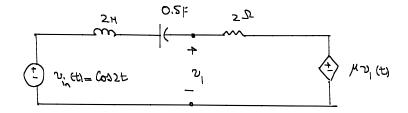

**Q1)** Consider the circuit shown below. It is desired to find the voltage  $v_1(t)$ .

- a) Using a method of your choice, determine the range of  $\mu$  for which the solution using phasors will remain valid.

- b) State what nature of discrepancy between the phasor solution and the actual response when  $\mu$  is outside this range.

**Q2)** The initial condition of the inductor in the circuit shown below is zero, i.e.  $i_L(0^-) = 0$  A. Determine the capacitance C and its initial condition  $v_C(0^-)$  so that  $i_R(t) = 0$  for  $t \ge 0$ .

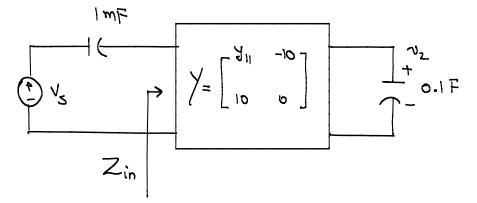

Q3) The s-domain admittance parameters of the following two-port network (initial conditions are all zero) are given below.

- a) Find  $y_{11}$  so that the impedance looking into port 1 ( $Z_{in}$ ) becomes equivalent to that of a 1-mH inductor.

- b) Determine the gain  $v_2/v_s$  in s-domain.

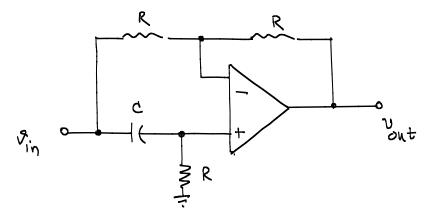

Q4) Consider the circuit shown below. The op-amp is assumed to be ideal.

- a) Determine the impulse response of the circuit in the time domain.

- b) Determine what kind of filter this circuit is.

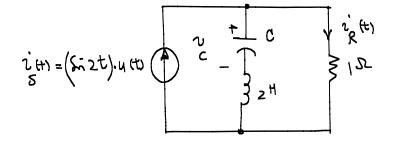

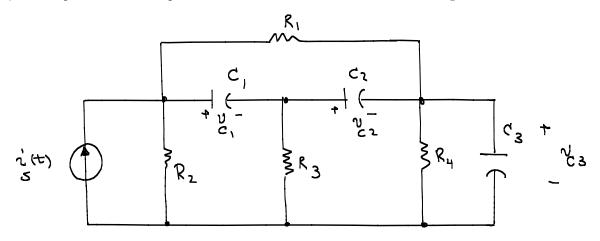

**Q5)** Develop a set of state equations in the standard form for the following circuit.

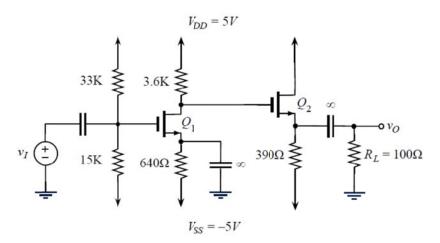

**Q6)** For the circuit shown,  $k_n = 1 \text{mA/V}^2$ ,  $V_t = 0.75 \text{V}$ ,  $V_{DD} = 5 \text{V}$ ,  $V_{SS} = -5 \text{V}$ , and  $I_{DI} = 1.25 \text{mA}$ . Determine the maximum signal swing at the output  $v_O$ .

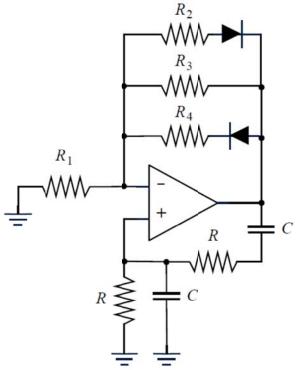

$\mathbf{Q7}$ ) For the given sinusoidal oscillator circuit, assume the operational amplifier and the diodes are ideal.

- (a) Derive an expression for the oscillator frequency  $\omega_0$ .

- (b) Select values of all circuit components such that the circuit oscillates at a frequency of 10kHz.

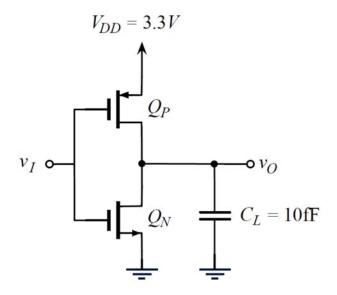

**Q8**) The CMOS inverter with  $V_{DD} = 3.3$ V drives a load capacitance  $C_L = 10$  fF. The transistors have the properties  $k_n' = 150 \mu A/V^2$ ,  $k_p' = 50 \mu A/V^2$  and  $V_{tn} = |V_{tp}| = 0.5$ V.

- (c) If the circuit operates at a frequency of 10MHz, what is the dynamic power dissipated?

- (d) It is observed that the peak short-circuit current for the inverter is 150µA. If the transistors have a length L = 0.18µm, and are sized such that  $V_M = V_{DD}/2$ , determine the width of the gate of each transistor.

- (e) Determine the propagation delay  $t_p$  for the inverter.

**Q9**) Assume we have two square waves with 5V p-p amplitude. Design a circuit that will output a voltage that is proportional to the phase shift difference between the two square-waves over a 0.5 radian range. You are free to use both digital and analog circuits. You are free to choose the initial phase difference between the two signals.

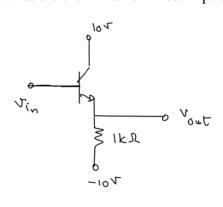

**Q10**) For the following circuit, what are the limits for linear input versus output?